发布日期:2023-09-22

一、引言

FPGA(Field Programmable Gate Array,现场可编程门阵列)是一种可编程逻辑芯片,能够根据特定应用的需求进行配置和重新编程。在FPGA中,RAM(Random Access Memory,随机存取存储器)是一种重要的组件,用于存储和读取数据。RAM的背景可以追溯到计算机体系结构和存储技术的发展。RAM是一种易失性存储器,意味着当电源关闭时,存储在其中的数据将丢失。然而,它具有快速的读写速度和随机访问能力,使其成为处理器和计算系统中重要的组成部分。

在FPGA中,RAM被用于实现数据存储、缓存和中间结果的存储等功能。它可以作为数据缓冲区,存储输入、输出和中间数据,以提高系统性能。RAM还可以用于存储程序指令,支持动态指令修改和灵活的指令执行。FPGA中的RAM通常以块RAM(Block RAM)或分布式RAM(Distributed RAM)的形式存在。块RAM是专用的存储区域,具有较大的容量和更高的性能,适用于大规模数据存储和处理。分布式RAM则是通过利用FPGA内部的逻辑资源来实现的,适用于小规模的数据存储和临时变量。随着FPGA技术的不断发展,RAM的容量和性能也在不断提升。现代FPGA中的RAM模块可以提供更大的存储容量、更快的访问速度和更高的并行性能,为各种应用提供了更强大的数据存储和处理能力。

二、技术原理

1、静态RAM(SRAM): 静态RAM使用触发器电路(通常是双稳态触发器)来存储每个位的数据。每个位都由一个存储器单元和相关的访问线组成。SRAM的技术原理如下:

1)存储单元:每个存储单元由一个双稳态触发器构成,其中包含一个电容和至少六个晶体管。这些晶体管构成了一个存储电荷的闭环,保持数据的稳定性。

2)读操作:当读取数据时,访问线通过传输门与存储单元连接。如果访问线上的电平为高(1),则存储单元中的电荷通过传输门传递到读取线上,表示数据位为1。如果访问线上的电平为低(0),则存储单元中的电荷不发生变化,表示数据位为0。

3)写操作:当写入数据时,访问线上的电平控制传输门的开关。如果写入线上的电平为高(1),则数据位被设置为1,电荷通过传输门传递到存储单元。如果写入线上的电平为低(0),则数据位被设置为0,存储单元中的电荷被清空。

2、动态RAM(DRAM): 动态RAM使用电容器来存储每个位的数据,因此需要定期刷新以保持数据的稳定性。DRAM的技术原理如下:

1)存储单元:每个存储单元由一个电容和一个访问晶体管组成。电容器充电或放电来表示数据位的状态。

2)读操作:当读取数据时,访问线通过访问晶体管与存储单元的电容连接。电容器的充放电状态决定了数据位的状态。读取操作会导致电容器的放电,因此需要在读操作之后进行刷新。

3)写操作:当写入数据时,访问线上的电平控制访问晶体管的开关。如果写入线上的电平为高,则电容器充电,表示数据位为1。如果写入线上的电平为低,则电容器放电,表示数据位为0。

三、实现步骤

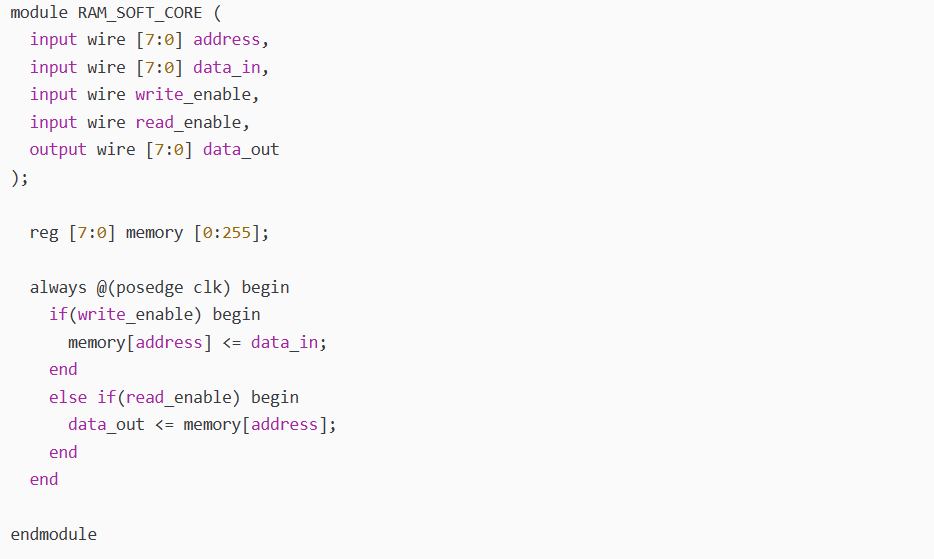

1)以下是一个使用Verilog语言编写的RAM软核的示例:

在这个示例中,RAM_SOFT_CORE模块接收了一个8位的地址(address)、一个8位的输入数据(data_in)、一个写使能信号(write_enable)、一个读使能信号(read_enable),并输出一个8位的数据(data_out)。该模块内部包含一个具有256个8位存储单元的内存数组(memory)。

在时钟上升沿触发的always块中,根据写使能信号和读使能信号的状态,进行相应的操作。当写使能信号为高时,将输入数据写入到指定地址的内存单元中。当读使能信号为高时,将指定地址的内存单元中的数据输出。

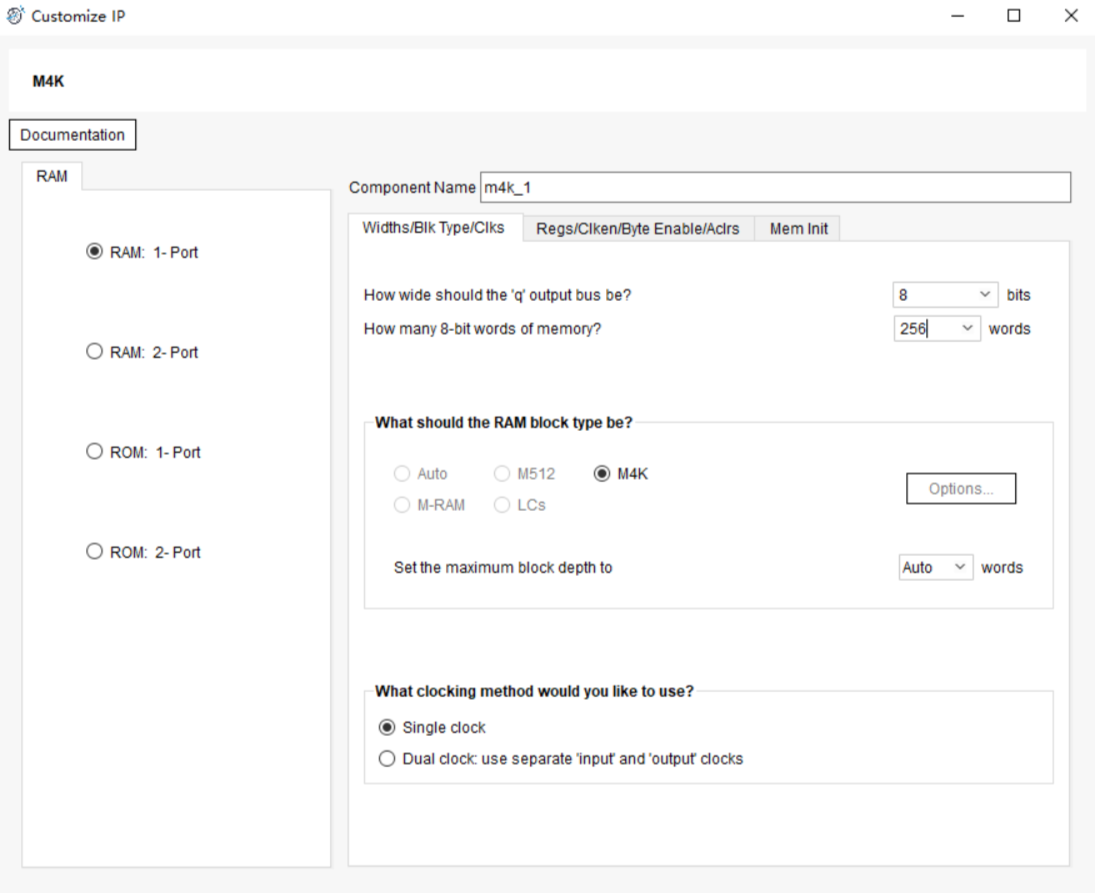

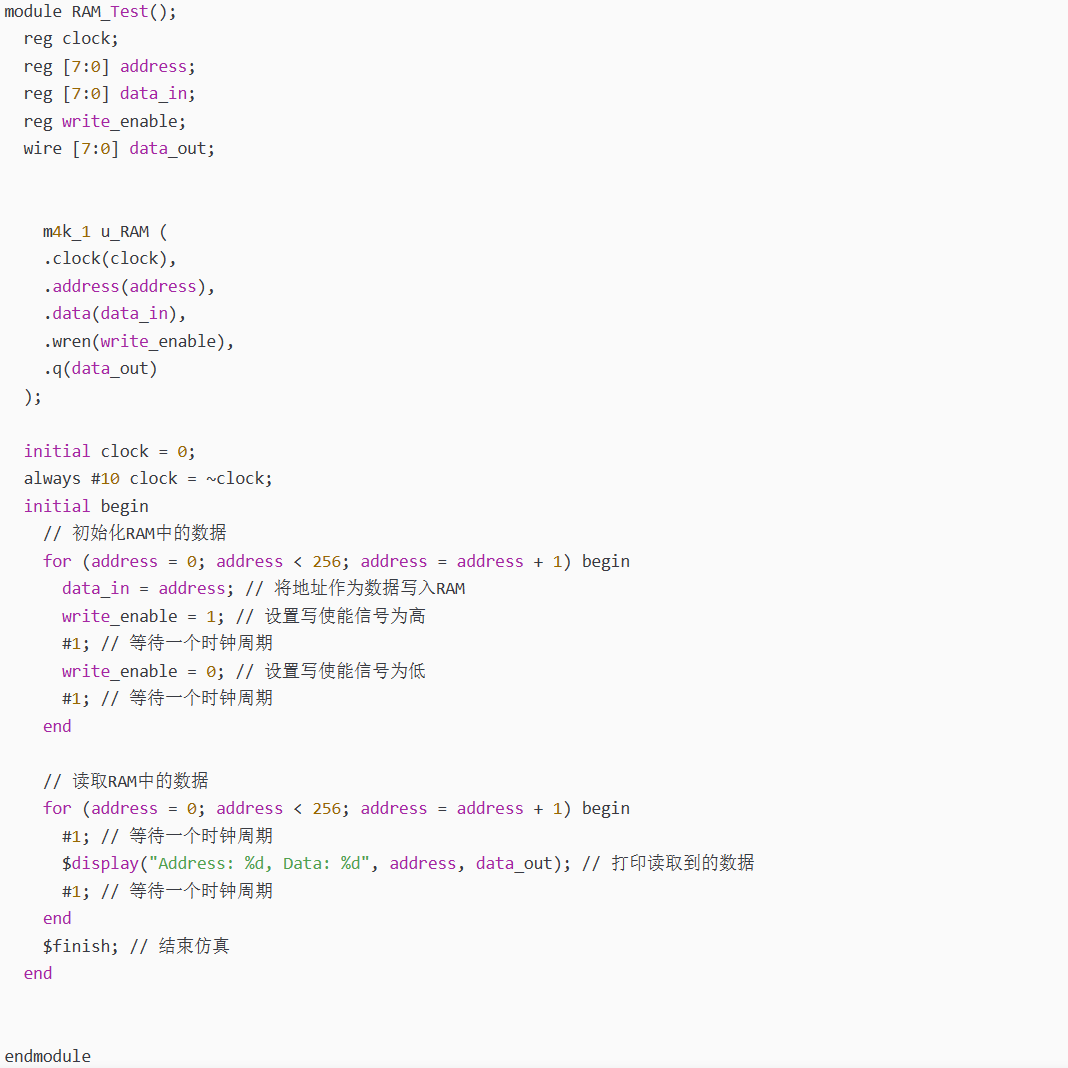

2)使用中科亿海微eLinx工具进行开发:

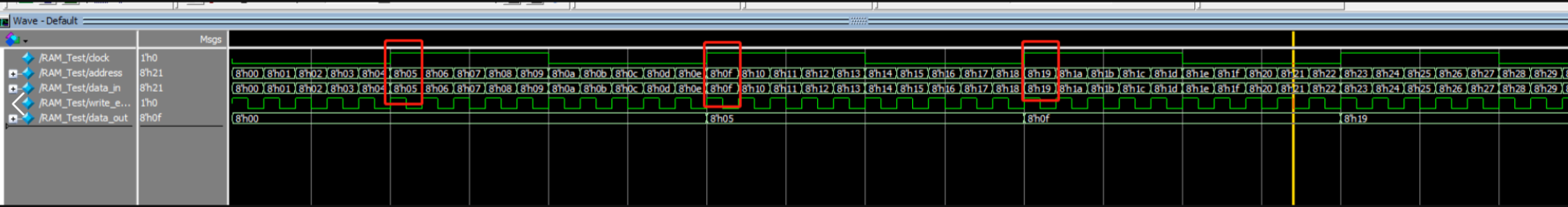

四、实验结果

五、应用场景

1、数据存储:FPGA 中的 RAM 可用于存储数据,包括配置数据、算法数据、图像数据等。通过将数据存储在 RAM 中,可以实现快速的读写操作,提高系统性能。

2、缓存:RAM 可用作缓存存储器,用于临时存储频繁访问的数据。通过使用 RAM 缓存数据,可以减少对外部存储器的访问次数,提高系统响应速度。

3、图像处理:FPGA 中的 RAM 可用于存储图像数据,包括图像帧缓冲区、图像滤波器系数等。通过使用 RAM 存储图像数据,可以实现高速的图像处理和实时视频处理。

4、数据交换:RAM 可用于在不同模块之间交换数据。例如,多个处理模块可以通过共享一个 RAM 存储区域来传递数据,实现数据的共享和交互。

5、存储器控制器:FPGA 中的 RAM 可以用于实现存储器控制器,包括读写控制、地址解码、数据缓冲等功能。通过编写相应的控制逻辑,可以实现对 RAM 存储器的灵活控制和管理。

6、FIFO 缓冲器:RAM 可以用作 FIFO(先进先出)缓冲器,用于数据的临时存储和流控制。FPGA 中的 RAM 可以提供高速的读写操作,适用于数据流处理和通信应用。

六、总结

内存资源:FPGA中的RAM是有限的资源,因此需要根据实际需求合理规划和分配内存资源。考虑到性能和资源占用方面的平衡,需要确定所需的RAM容量和数量,并确保不会超出FPGA的可用资源。

时序约束:RAM读写操作需要满足一定的时序要求,包括读写时钟速度、地址稳定时间、数据保持时间等。在设计时,需要根据所选RAM的规格和FPGA的限制,设置适当的时序约束以确保数据的正确读写。

存储器控制器设计:在FPGA中使用RAM时,通常需要设计相应的存储器控制器来管理读写操作。存储器控制器应该能够有效地处理读写请求,并确保正确的时序和数据一致性。

内存访问冲突:当多个模块同时访问同一个RAM时,可能会出现内存访问冲突的问题。为了避免冲突,需要合理规划内存访问的时序或者引入合适的同步机制,例如互斥锁或流水线等。

数据一致性:在多模块或多时钟域的系统中,由于FPGA中的RAM是异步存储器,需要特别注意数据一致性的问题。确保在不同模块之间进行数据交换时,采用合适的同步策略和数据验证机制,以避免数据错误或不一致的情况发生。

信号布线:在FPGA中使用RAM时,需要合理布局和布线RAM的输入输出信号。根据设计需求,将RAM模块和相关信号放置在合适的位置,以最小化信号传输延迟和功耗。

参考文献

1."Computer Organization and Design: The Hardware/Software Interface" by David A. Patterson and John L. Hennessy - 这本书是计算机组织与设计的经典教材,其中包含了关于RAM的基本概念、结构和操作。

2."Memory Systems: Cache, DRAM, Disk" by Bruce Jacob, Spencer Ng, and David Wang - 这本书深入介绍了存储系统的各个层次,包括RAM的组织、层次结构、性能和优化。

3."High-Speed Digital Design: A Handbook of Black Magic" by Howard W. Johnson and Martin Graham - 这本书讲解了在高速数字设计中遇到的各种挑战,其中包括关于RAM接口和时序设计的内容。

4."RAM Design and Application" by Ashok Bindra - 这本书重点介绍了RAM的设计和应用,包括静态RAM(SRAM)和动态RAM(DRAM)的原理、布局和性能优化。